# Novel Linear Analog-Adder Using a-IGZO TFTs

Pydi Ganga Bahubalindruni<sup>a,c</sup>, Vítor Grade Tavares<sup>b</sup>, Elvira Fortunato<sup>a</sup>, Rodrigo Martins<sup>a</sup>, Pedro Barquinha<sup>a</sup> i3N/CENIMAT, Department of Materials Science and Technology,

Universidade NOVA de Lisboa and CEMOP-UNINOVA, Campus de Caparica, 2829-516 Caparica, Portugal Email: p.bahubalindruni@campus.fct.unl.pt

INESC TEC and Faculty of Engineering, University of Porto, Campus FEUP,

Rua Dr. Roberto Frias, 378, 4200-465 Porto, Portugal

IIIT-Delhi, Okhla Industrial Estate, Phase III, New Delhi, India - 110020

Abstract—A novel linear analog adder is proposed only with ntype enhancement IGZO TFTs that computes summation of four voltage signals. However, this design can be easily extended to perform summation of higher number of signals, just by adding a single TFT for each additional signal in the input block. The circuit needs few number of transistors, only a single power supply irrespective of the number of voltage signals to be added, and offers good accuracy over a reasonable range of input values. The circuit was fabricated on glass substrate with the annealing temperature not exceeding 200° C. The circuit performance is characterized from measurements under normal ambient at room temperature, with a power supply voltage of  $12\,\mathrm{V}$  and a load of  $\approx 4\,\mathrm{pF}$ . The designed circuit has shown a linearity error of 2.3% (until input signal peak to peak value is 2 V), a power consumption of 78  $\mu$ W and a bandwidth of  $\approx$ 115 kHz, under the worst case condition (when it is adding four signals with the same frequency). In this test setup, it has been noticed that the second harmonic is 32 dB below the fundamental frequency component. This circuit could offer an economic alternative to the conventional approaches, being an important contribution to increase the functionality of large area flexible electronics.

Index Terms-Analog adder, IGZO TFTs, and linearization.

## I. INTRODUCTION

The attractive features of Indium-Gallium-Zinc-Oxide thinfilm transistors (IGZO TFTs) are low-temperature fabrication, good optical transparency, relative high mobility [1], when compared to other TFT technologies, such as, a-Si:H and OTFT. Analog mixed-signal circuits with IGZO TFT technology [2], [3], [4] have already gained significant interest because of their potential applications in various fields [5], [6], [7].

The realization of analog adders is of considerable interest for most the linear analog circuits [8], neural networks [9], continuous time signal processing applications [10] and oversampling data converters [11]. Though significant work was reported with CMOS technology [12], [13], [14], there was no attempt yet to realize it with IGZO TFTs. One of the possible reasons for this could be lack of stable and reproducible complementary (p-type) devices.

This paper presents a novel linear analog adder only with ntype IGZO TFTs. This design provides a simple way of adding 'n' number of signals to produce a single output without using any operational amplifier. Source degeneration technique is used to improve linearity performance of the circuit. In addition, care has been taken to compensate the gain loss from this linearization method, by using a simple output stage. This design used only a few number of TFTs and a single power supply.

Rest of the paper is organized as follows: Section II describes the device fabrication details. Section III presents circuit design and section IV explains the measured results. Finally, conclusions are drawn in section V.

#### II. FABRICATION

The TFTs employed in the current work have a bottomgate inverted staggered structure, being fabricated in Corning Eagle glass substrates. Gate electrode was e-beam evaporated and patterned by lift-off, consisting of 60 nm thick Ti/Au. A 250 nm thick dielectric following a multilayer approach consisting of SiO<sub>2</sub> + Ta<sub>2</sub>O<sub>5</sub> + SiO<sub>2</sub> was then r.f. sputtered and patterned using reactive ion etching. This was followed by the deposition and lift-off patterning of r.f. sputtered IGZO layer, 40 nm thick. Source drain electrodes were processed with Ti/Au following similar procedure as described for gate electrode. Finally, devices/circuits were passivated with spincoated SU8 transparent resist. Annealing in air at 200°C for 1 hour was carried out prior passivation. In the designed circuit, all the TFTs have a channel length of  $20 \,\mu m$  and a gate to source/drain overlap of  $5 \mu m$ . These devices have shown a mobility of 17.4 cm<sup>2</sup>/V·s, leakage current in the order of pA, and a turn-on voltage close to 0 V.

It has to be noted that the transparent devices and circuits can be achieved by employing transparent conductive oxides (e.g. IZO, ITO) as gate, source and drain electrodes and interconnects. However, this work used Ti/Au for source/drain as it can allow easy wire-bonding, which in turn facilitates flexibility in testing.

## III. CIRCUIT DESIGN

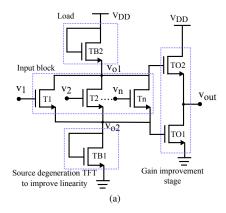

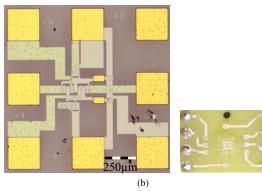

The proposed circuit schematic and its micrograph before and after wire-bonding are presented in Fig. 1. This circuit is capable of adding an arbitrary number of signals. However, the fabricated circuit was designed to add up to four voltage signals. As it can be noticed from Fig. 1a, in order to enhance the ability of the circuit to add more number of voltage signals, a single TFT should be added in the input block (parallel to T1, T2 or Tn) for each additional signal without any other

changes. It can be understood that the circuit does not impose limitations on the number of signals to be added.

Fig. 1. Novel adder: (a) Circuit schematic (b) Micrograph of the fabricated circuit and photo of wire bounded circuit.

In Fig. 1a, the diode connected TFT (TB1) acts as a source degeneration resistor with an equivalent impedance of  $\frac{1}{g_{mB}}$ , where  $g_{mB}$  is the transconductance of TB1. This TFT helps in improving the linearity performance of the circuit due to the negative voltage feedback. However, this imposes a limitation on the gain of the circuit, which is compensated by the output stage formed by TO1 and TO2.

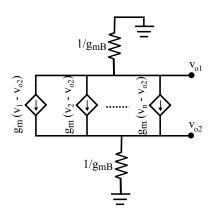

Fig. 2. Small signal equivalent of the circuit (excluding the output stage).

The small-signal equivalent circuit, formed by transistors

T1 to Tn ,TB1 and TB2, is shown in Fig. 2. As the channel length of TFTs is relatively high, channel length modulation is ignored in the analysis. Assuming the same aspect ratios for all transistors, T1 to Tn, and under similar bias conditions, they will share the same small-signal transconductance value  $g_m$ , while the load and source degeneration transistors will be defined by  $g_{mB}$ . With the help of Fig. 2, the relationship between the output and input voltages can be derived as below,

$$\begin{array}{rcl} v_{o1} & = & -v_{o2} & & & & \\ v_{o2} & = & \frac{1}{g_{mB}} \left[ g_m(v_1 - v_{o2}) + g_m(v_2 - v_{o2}) + \dots + g_m(v_n - v_{o2}) \right] \\ v_o & = & v_{o1} - v_{o2}, \quad \text{hence} \\ v_o & \propto & -(v_1 + v_2 + \dots + v_n) \end{array}$$

For the specific case, when  $g_{mB}=ng_m$  i.e.,  $W_{(TB1/TB2)}=nW_{(T1,T2..Tn)},$  equation (1) can be reduced to

$$v_o = \frac{1}{n} [v_1 + v_2 + \dots + v_n]$$

(2)

From (1), it can be noticed that this circuit can perform the summation of multiple signals. The average of the input signals can also be obtained as per (2).

#### IV. RESULTS AND DISCUSSION

The circuit is characterized under normal ambient at room temperature. Circuit simulations were carried out with an inhouse model. Measurements were taken with a power supply of 12 V and a load of approximately 4 pF (load is formed with an external unity gain buffer, whose frequency response is much higher than the measured range i.e., 1 MHz). Single channel arbitrary function generators (AFG3021B) and four channel digital storage oscilloscope (DS2024B) were used for the measurements.

The circuit is tested with the following stimulus.

$$v1 = 5 + Asin(2\pi f_1 t),$$

$$v2 = 5 + Asin(2\pi f_2 t),$$

$$v3 = 5 + Asin(2\pi f_3 t),$$

$$v4 = 5 + Asin(2\pi f_4 t).$$

(3)

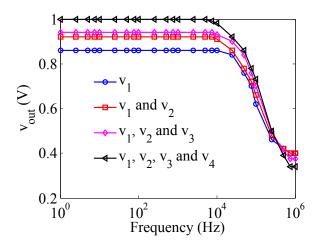

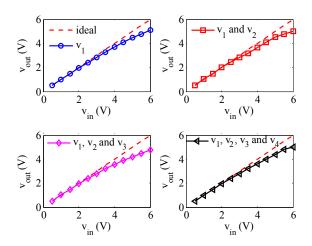

Its frequency response is presented in Fig. 3, when different number of input signals are applied to the adder. The circuit has shown approximately 115 kHz bandwidth and  $78\,\mu\text{W}$  power consumption, when all the input signals are applied.

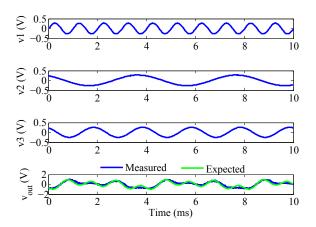

The normalized measured response is compared and validated with the expected response as shown in Fig. 4, when  $f_1 = 250 \,\mathrm{Hz}$ ,  $f_2 = 500 \,\mathrm{Hz}$  and  $f_3 = 1000 \,\mathrm{Hz}$  and v4 is a constant bias. Ideal and measured linearity response of the circuit is presented in Fig. 5, when different number of input signals are applied. The circuit shows a linearity error < 2.3%, until the input signal peak-to-peak value is  $2 \,\mathrm{V}$ . As expected,

Fig. 3. Measured frequency response of the circuit with different number of input signals.

Fig. 4. Circuit characterization from measured and expected response in normalized form.

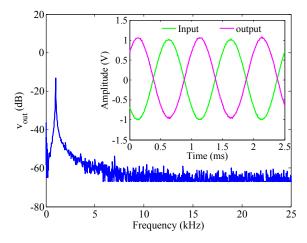

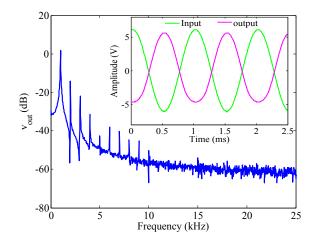

linearity error increases with respect to the increase in the input signal amplitude, which is due to the nonlinear behavior of the TFTs. The measured output signal (in inset) and its corresponding FFT are presented in Fig. 6 and 7, when the stimulus from equation (4) is applied, with all the signals have same frequency of 1 kHz, and a peak-to-peak amplitude of 2V and 6V, respectively. In case of Fig. 6, the second harmonic is 32 dB below the fundamental component, on the other hand, Fig. 7 shows high harmonic distortion (18 dB difference between the fundamental and second harmonic component) with increased input signal amplitude. Table I presents the difference between the fundamental and second harmonic components, when different number of input signals (amplitude 2 V peak-to-peak) are applied to the circuit. From these results it can be understood that the circuit shows minimum harmonic distortion for reasonable input signals amplitude.

Fig. 5. Measured linearity response of the circuit with different number of input signals.

Fig. 6. Measured circuit response, when all the input signals peak to peak value is  $2\,\mathrm{V}$  and frequency is  $1\,\mathrm{kHz}.$

Fig. 7. Measured circuit response, when all the input signals peak to peak value is  $6\,\mathrm{V}$  and frequency is  $1\,\mathrm{kHz}$ .

TABLE I

DIFFERENCE BETWEEN FIRST AND SECOND HARMONIC LEVELS

| No. of signals | Difference between first and second harmonic (dB) |

|----------------|---------------------------------------------------|

| 1              | 42                                                |

| 2              | 36                                                |

| 3              | 35                                                |

| 4              | 32                                                |

### V. CONCLUSIONS

For the first time a novel linear and low-power analog adder circuit with n-type IGZO TFTs is designed and characterized from the measurements, which was fabricated at low temperature (200°C). The proposed circuit does not need any operations amplifier. Further, the circuit has the ability to add up to four signals and the design can be easily extended for more number of input signals without any major changes. Linearity performance of the circuit was improved by using a simple source degeneration approach (using a diode connected transistor). Gain compensation was obtained with a simple output stage. From measurements, it was noticed that the linearity error is less that 2.3% up to the input signals with a peak-to-peak voltage values of 2 V, when adding four signals. Under the same testing condition, the circuit has shown a power consumption of  $78 \,\mu\text{W}$  and a bandwidth of  $\approx 115 \,\text{kHz}$ .

#### ACKNOWLEDGMENT

The first author would like to thank Prof. Joao Goes for his valuable suggestions. This work is funded by FEDER funds through the COMPETE 2020 Programme and National Funds through FCT - Portuguese Foundation for Science and Technology under the Project Nos. UID/CTM/50025/2013 and EXCL/CTM-NAN/0201/2012. The work has also received funding from the European Communities 7th Framework Programme under grant agreement ICT-2013-10-611070 (i-FLEXIS project) and from H2020 program under ICT-03-2014-644631 (ROLL-OUT project).

## REFERENCES

- K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano, and H. Hosono, "Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors," *Nature*, vol. 432, no. 7016, pp. 488–492, Oct 2004.

- [2] P. Ganga Bahubalindruni, B. Silva, V. Grade Tavares, P. Barquinha, N. Cardoso, P. Guedes de Oliveira, R. Martins, and E. Fortunato, "Analog Circuits With High-Gain Topologies Using a-GIZO TFTs on Glass," *IEEE/OSA J. Display Technol.*, vol. 11, no. 6, pp. 547–553, June 2015.

- [3] C. Zysset, N. Munzenrieder, L. Petti, L. Buthe, G. Salvatore, and G. Troster, "IGZO TFT-Based All-Enhancement Operational Amplifier Bent to a Radius of 5 mm," *IEEE Electron Device Lett.*, vol. 34, no. 11, pp. 1394–1396, 2013.

- [4] D. Raiteri, F. Torricelli, K. Myny, M. Nag, B. Van der Putten, E. Smits, S. Steudel, K. Tempelaars, A. Tripathi, G. Gelinck, A. van Roermund, and E. Cantatore, "A 6b 10MS/s current-steering DAC manufactured with amorphous Gallium-Indum-Zinc-Oxide TFTs achieving SFDR > 30dB up to 300kHz," in *International Solid-State Circuits (ISSCC)*, Feb 2012, pp. 314–316.

- [5] J. H. Lee, D. H. Kim, D. J. Yang, S. Y. Hong, K. S. Yoon, P. S. Hong, C. O. Jeong, H. S. Park, S. Y. Kim, S. K. Lim, S. S. Kim, K. S. Son, T. S. Kim, J. Y. Kwon, and S. Y. Lee, "42.2: World's Largest (15-inch) XGA AMLCD Panel Using IGZO Oxide TFT," SID Symposium Digest of Technical Papers, vol. 39, no. 1, pp. 625–628, 2008.

- [6] B. D. Yang, J. M. Oh, H. J. Kang, S. H. Park, C. S. Hwang, M. K. Ryu, and J. E. Pi, "A Transparent Logic Circuit for RFID Tag in a-IGZO TFT Technology," *ETRI Journal*, vol. 35, no. 4, pp. 610–616, 2013.

- [7] H. Ozaki, T. Kawamura, H. Wakana, T. Yamazoe, and H. Uchiyama, "20- uw operation of an a-IGZO TFT-based RFID chip using purely NMOS "active"; load logic gates with ultra-low-consumption power," in *Symposium on VLSI Circuits (VLSIC)*, June 2011, pp. 54–55.

- [8] M. Cheng and C. Toumazou, "Linear composite MOSFET: theory, design, and applications," *IEEE Trans. Circuits Syst. I*, vol. 40, no. 5, pp. 297–306, May 1993.

- [9] M. Al-Nsour and H. Abdel-Aty-Zohdy, "Analog computational circuits for neural network implementations," in *International Conference on Electronics, Circuits and Systems*, vol. 1, 1999, pp. 299–302.

- [10] N. Futane, S. RoyChowdhury, C. RoyChaudhuri, and H. Saha, "Analog asic for improved temperature drift compensation of a high sensitive porous silicon pressure sensor," *Analog Integrated Circuits and Signal Processing*, vol. 67, no. 3, pp. 383–393, 2011.

- [11] A. Gharbiya and D. Johns, "On the implementation of input-feedforward delta-sigma modulators," *IEEE Transactions on Circuits and Systems II:* Express Briefs, vol. 53, no. 6, pp. 453–457, June 2006.

- [12] H. Chaoui, "Cmos analogue adder," *Electronics Letters*, vol. 31, no. 3, pp. 180–181, Feb 1995.

- [13] S. Tsay and R. Newcomb, "A neural-type pool arithmetic unit," in *IEEE International Sympoisum on Circuits and Systems*, vol. 5, Jun 1991, pp. 2518–2521.

- [14] A. Diaz-Sanchez and J. Ramirez-Angulo, "A compact high frequency VLSI differential analog adder," in *IEEE 39th Midwest symposium on Circuits and Systems*, vol. 1, Aug 1996, pp. 21–24.