# Transparent Current Mirrors With a-GIZO TFTs: Neural Modeling, Simulation and Fabrication

Pydi Ganga Bahubalindruni, Vítor Grade Tavares, Pedro Barquinha, Cândido Duarte, Pedro Guedes de Oliveira, Rodrigo Martins, and Elvira Fortunato

Abstract—This paper characterizes transparent current mirrors with n-type amorphous gallium—indium—zinc—oxide (a-GIZO) thin-film transistors (TFTs). Two-TFT current mirrors with different mirroring ratios and a cascode topology are considered. A neural model is developed based on the measured data of the TFTs and is implemented in Verilog-A; then it is used to simulate the circuits with Cadence Virtuoso Spectre simulator. The simulation outcomes are validated with the fabricated circuit response. These results show that the neural network can model TFT accurately, as well as the current mirroring ability of the TFTs.

*Index Terms*—Transparent current mirrors, amorphous gallium–indium–zinc–oxide thin-film transistor (a-GIZO TFT), neural modeling.

# I. INTRODUCTION

MORPHOUS gallium-indium-zinc-oxide (a-GIZO) thin-film transistor (TFT) technology has potential industrial applications in large-area, low-cost transparent display technologies such as AMOLED [1] and ultra definition LCD [2]. Fabrication can be achieved at low temperature, followed by heat treatment not exceeding 200°C. Furthermore, the high electrical mobility 20 cm<sup>2</sup>/V·s [3] compared to other TFTs (a-Si:H : 1 cm<sup>2</sup>/V·s [4], organic TFT : 0.1–1 cm<sup>2</sup>/V·s [5]), make a-GIZO TFTs attractive for transparent and flexible electronics [6]. These are the motivating factors to build analog circuits for various types of sensing and display applications, which will be portable and economic, resulting in integrated circuits that avoid interfacing problems. The analog circuit design is limited due to the lack of stable p-type TFT and unavailability of built-in libraries for the active and passive

Manuscript received May 04, 2013; revised July 01, 2013; accepted July 17, 2013. Date of publication July 30, 2013; date of current version November 18, 2013. This work was supported by the ERDF through the Programme COMPETE and by the Portuguese Government through FCT—Foundation for Science and Technology under Projects CMU-PT/SIA/0005/2009, FCOMP-01-0124-FEDER-013070, and PEST-C/CTM/LA0025/2011 strategic project, and also by the European Research Council through the Advanced Grant INVISIBLE (ERC-2008-AdG 228144. The work of P. G. Bahubalindruni and C. Duarte is also supported in part by the FCT under Grants BD/62678/2009 and BD/28163/2006, respectively.

P. G. Bahubalindruni, V. G. Tavares, C. Duarte, and P. G. de Oliveira are with INESC TEC (formerly INESC Porto) and Faculty of Engineering, University of Porto, Campus FEUP, 4200-465 Porto, Portugal e-mail: (vgt@fe.up.pt).

P. Barquinha, R. Martins, and E. Fortunato are with CENIMAT/I3N, Department of Materials Science, Faculty of Science and Technology, FCT, Universidade Nova de Lisboa, and CEMOP-UNINOVA, 2829-516 Caparica, Portugal.

Color versions of one or more of the figures are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JDT.2013.2275251

components. Nevertheless, few circuits are reported, mostly with depletion type TFTs such as a shift register [7] and a 6-bit current-steering DAC [8].

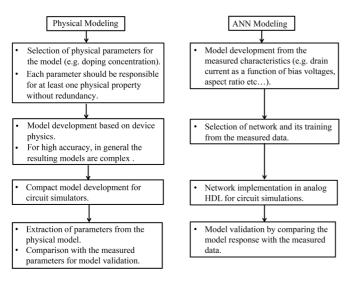

In order to design and simulate circuits, punctilious device models are necessary to predict the device behavior during simulations. Models based on device physics are generally used for circuit design. Nevertheless, physical models are complex and time consuming to develop. Especially physical modeling is not a good choice for novel technologies, such as a-GIZO, which are not yet well matured, and where experiments are still going on to ensure better behavior, either by changing device structure [9], materials for electrodes or processing conditions. All these factors certainly impact the density of states and charge carrier flow in the device. Whenever there is a change in any of the aforementioned factors, the corresponding device physics need to be studied and a new model needs to be developed. Possible alternative methods are table-based and neural network models that are built from the device measured characteristics. However, accurate table-based models [10] demand huge memory. Artificial Neural Network (ANN) modeling overcomes all these drawbacks without compromising performance. When quicker circuit design is important, with new devices as a-GIZO TFT, a simple, accurate and continuous model, with less development time is desired. ANNs have all these properties, and in fact, multilayer feedforward network has already been successfully applied to model MOSFETs, as proposed in [11]. The current work includes the complete device behavior, i.e., intrinsic and extrinsic, by taking the series resistance  $(R_s + R_d)$  of source and drain electrodes into account. If only the intrinsic behavior of the device needs to be modeled, the impact of  $R_s + R_d$  should be deembeded from the measured data. Then, the network needs to be trained with this new data. The extraction method of  $R_s + R_d$ should basically follow the same procedure as in physical modeling. General steps in physical and ANN based modeling approaches are shown in Fig. 1.

Current mirrors are important functional blocks in analog circuit design, which find applications in providing bias, as an active load and pixel driving circuits in OLED displays [12]. ZTO TFT-based current mirrors have been already reported in the past, but with metallic electrodes and requiring a high post-processing temperature of 400 °C [13]. In this work we are reporting simple current mirrors with two TFTs having different mirroring ratios and a cascode mirror, all based on fully transparent GIZO-TFTs with processing temperatures not exceeding 200 °C. As a first step, an ANN model is developed from the measured data of the TFTs, being then implemented in Verilog-A for circuit simulation using Cadence Virtuoso Spectre.

Fig. 1. General steps in physical and ANN based modeling methods.

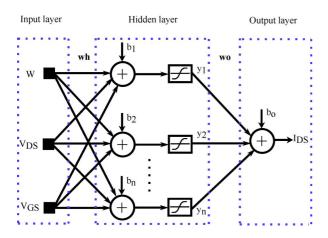

Fig. 2. Topology of the feedforward ANN model with a single hidden layer.

Finally, circuits are fabricated. A comparison of simulated, fabricated circuits and the expected results are presented to demonstrate the ANN modeling ability, as well as current mirroring capability of the a-GIZO TFTs.

## II. NEURAL MODELING

A multilayer feedforward network, with a single hidden layer and a sufficient number of neurons, is a universal approximator [14]. This is the minimum structure adopted in this work to minimize complexity, with the typical single-hidden layer topology as shown in Fig. 2. Backpropagation algorithm is used for training. The network learns the function that needs to be approximated from the training data (i.e.,  $I_{\rm DS}$  as a function of W,  $V_{\rm DS}$  and  $V_{\rm GS}$ ). The hidden layer neurons perform weighted summation followed by a limiting function, whereas the output neuron only performs a weighted summation (linear neuron). During the training phase, the network calculates the output from the given inputs in the forward direction. This is compared to the expected value and the error is propagated in the backward direction, which in turn modifies the weights and biases of the network to minimize the error. The network stops learning at a point when the validation error starts increasing.

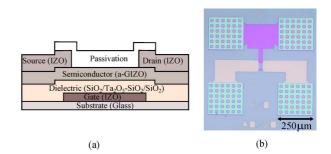

Fig. 3. Transparent a-GIZO TFTs: (a) Schematic of the device cross section, with a staggered bottom gate configuration (b) Micrograph of one isolated device, with  $W/L = 40/20 \ \mu m$ .

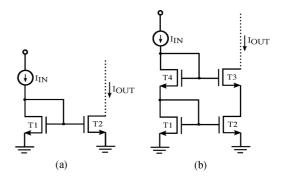

Fig. 4. Current mirrors schematics. (a) With two-TFTs. (b) Cascode.

Validation data is a portion of the input data that is not used to train the network, but just to verify the performance during training.

#### **III. CIRCUIT DESIGN AND FABRICATION**

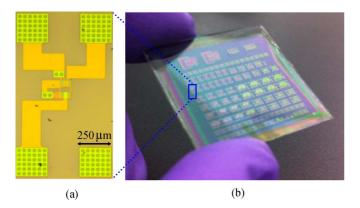

A Schematic of the cross-section and a micrograph of the fabricated transparent oxide TFTs are shown in Fig. 3. TFTs and circuits (integrated in the same  $2.5 \times 2.5$  cm<sup>2</sup> glass substrates) were fabricated with a staggered bottom gate structure and annealed at 200 °C. Gate, source and drain electrodes are based on  $In_2O_3$ -ZnO (IZO, 200 nm thick), the oxide semiconductor is Ga<sub>2</sub>O<sub>3</sub>-In<sub>2</sub>O<sub>3</sub>-ZnO (GIZO, 30 nm thick) and the dielectric layer is a multicomponent/multilayer structure composed of  $SiO_2/Ta_2O_5$ - $SiO_2/SiO_2$ , 350 nm thick. All these layers were deposited by RF magnetron sputtering without intentional substrate heating, using a home-made system (IZO) and an AJA ATC-1300F system (GIZO and dielectrics) [15]. The electrodes and the semiconductor were patterned using a lift-off process, while the dielectric was etched by reactive ion etching. More details regarding the processing and properties of these thin films and devices can be found in [16], [17]. On the top of this structure, a SU8 layer was spin-coated to act as a passivation layer, being patterned using conventional UV exposure and development processes [18].

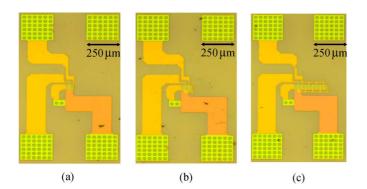

Schematics of two-TFT and cascode current mirrors are shown in Fig. 4(a) and (b) respectively. The two-TFT current mirrors micrographs of the fabricated circuits with different mirroring ratios are shown in Fig. 5. Different widths  $(W = 40 \ \mu\text{m}, 80 \ \mu\text{m}, \text{and } 320 \ \mu\text{m})$  have been used for the transistor T2 to obtain different mirroring ratios, with all the TFTs

Fig. 5. Micrographs of transparent two-TFT current mirrors based on a-GIZO TFTs. (a)  $(.W)_{T2} = 40 \ \mu\text{m}$ . (b)  $(W)_{T2} = 80 \ \mu\text{m}$ . (c)  $(W)_{T2} = 320 \ \mu\text{m}$ .

Fig. 6. (a) Micrograph of the transparent cascode current mirror based on a-GIZO TFTs with  $W/L = 40/20 \ \mu$ m for all the TFTs. (b) Entire glass substrate with circuits and isolated devices.

having a channel length (L) of 20  $\mu$ m. The cascode current mirror fabricated circuit is shown in Fig. 6(a). In this circuit, all TFTs (T1 to T4) have the same width (40  $\mu$ m). A photo of the glass substrate containing all the mentioned circuits, as well as isolated devices (TFTs), is shown in Fig. 6(b).

## IV. RESULTS AND DISCUSSION

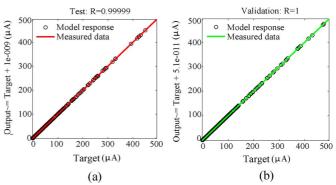

In order to develop the ANN model, measured data (averaged from two similar devices in two similar chips) are taken from the fabricated TFTs. The measurements have been performed using a semiconductor parameter analyzer Keithley 4200-SCS, and a Cascade Microtech M150 probe station under darkroom conditions. Matlab is used to train the network. The input data to the ANN is randomly divided into training (60%), validation (20%) and testing (20%). From the training data, the ANN learns the function that needs to be approximated. Validation data is used for stopping criteria, which ensures no over-fitting during the training phase. In its turn, testing data (never seen during training) are used to evaluate the generalization ability of the network. In the current case, a single hidden layer network with 25 neurons presented a good performance. Post-training values for testing and validation data are shown in Fig. 7(a) and (b) respectively. These results show good agreement between the measured data and modeled response as the regression factor

Fig. 7. ANN modeling response for a-GIZO TFTs. (a) Testing data performance. (b) Validation data performance.

Fig. 8. (a) Threshold voltage  $(V_T)$  calculation from the measured and simulated data (using the Verilog-A model—example with the 80  $\mu$ m TFT). (b) Measured and modeled transfer characteristics of transistor whose width is 320  $\mu$ m.

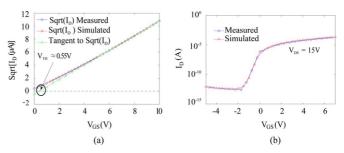

(R) is almost one. The resulting network is implemented in Verilog-A and it is used for all the aforementioned circuit simulations with Cadence Spectre simulator. The threshold voltages  $(V_T)$  of the TFTs can be calculated either from the simulated data using the developed Verilog-A model or from the measured data as shown in Fig. 8(a). Fig. 8(b) demonstrates very good agreement between measured and simulated transfer characteristics of a TFT at  $V_{\rm DS}$  15 V, where the TFT width is 320  $\mu$ m, reinforcing the validity of the model in the complete region of operation. However, a separate network has been used to model the region for  $V_{\rm GS} \leq 0$  V, as the current in the cut-off region spreads over several orders of magnitude. Nevertheless, one should note that the model is built with the intention of designing analog circuits, where generally,  $V_{\rm GS} \geq 0$  V.

For the current mirror circuits, ignoring channel-length modulation ( $\lambda$ ) due to long length of the devices and assuming that they are matched, the relation between input ( $I_{\rm IN}$ ) and mirrored ( $I_{\rm OUT}$ ) current can be expressed (for both topologies) as

$$\frac{I_{\rm OUT}}{I_{\rm IN}} = \frac{W2(V_{\rm GS} - V_{T2})^2 (1 + \lambda V_{DS2})}{W1(V_{\rm GS} - V_{T1})^2 (1 + \lambda V_{DS1})} \approx \frac{W2}{W1}$$

(1)

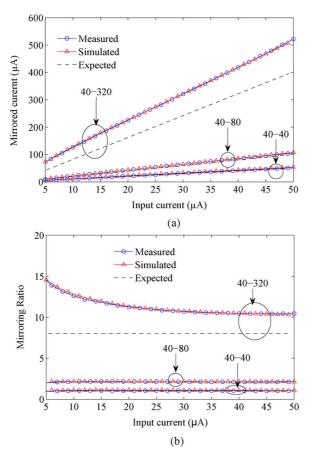

where  $V_{T1}$  and  $V_{T2}$  are the threshold voltages of the transistors T1 and T2, respectively. Fig. 9 shows the results for the two-TFT current mirrors with different mirroring ratios: simulation, expected, and measured responses are plotted (with mismatch removed by offsetting the simulation current). Similar re-

Fig. 9. Two-TFT current mirror response: expected, from neural model simulation and measured response with fabricated circuits. (a) Mirrored current. (b) Mirroring ratios.

| TABLE     | 11     |

|-----------|--------|

| MIRRORING | RATIOS |

| Mirrors   | 40-40 | 40-80 | 40-320 | Cas (20V) | Cas (22.5V) |

|-----------|-------|-------|--------|-----------|-------------|

| Expected  | 1     | 2     | 8      | 1         | 1           |

| Simulated | 1.093 | 2.149 | 11.43  | 1.011     | 1.017       |

| Measured  | 1.041 | 2.135 | 11.7   | 0.997     | 0.997       |

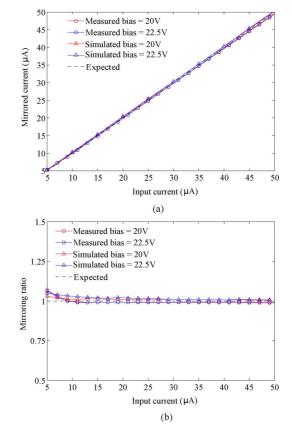

sults for the cascode current mirror, at different bias voltages, are shown in Fig. 10.

The average mirroring ratios of all the current mirrors are listed in Table I. Results show good agreement between the metrics (expected, simulated and measured) at lower mirroring ratios, whereas at higher mirroring ratio, there is a higher mirrored current, which is related to the fingered layout of output the transistor that tends to have a lower threshold-voltage. Nevertheless, the simulation results capture the non-ideal behavior properly. For the 40–320 current mirror, the negative slope in Fig. 9(b) is caused by a threshold-voltage mismatch between the input and output transistors.

## V. CONCLUSION

Current mirror circuits based on fully transparent a-GIZO TFTs annealed at 200 °C are demonstrated. A neural model is developed from the measured data of the TFTs and implemented in Verilog-A. This model's response is in good agreement with

Fig. 10. Cascode current mirror response at different bias voltages: expected, from neural model simulation and measured response with fabricated circuits. (a) Mirrored current. (b) Mirroring ratios.

the measured data. Circuits have been simulated with the developed model using Cadence Spectre simulator. When the simulation results are compared to the fabricated circuits' response, they reveal a good degree of prediction capability for the actual transistor behavior within the circuit operation.

# REFERENCES

- [1] J. Y. Kwon, K. S. Son, J. S. Jung, T. S. Kim, M. K. Ryu, K. B. Park, B. W. Yoo, J. W. Kim, Y. G. Lee, K. C. Park, S. Y. Lee, and J. M. Kim, "Bottom-gate gallium indium zinc oxide thin-film transistor array for high-resolution AMOLED display," *IEEE Electron Device Lett.*, vol. 29, no. 12, pp. 1309–1311, Dec. 2008.

- [2] N. Gong, C. Park, J. Lee, I. Jeong, H. Han, J. Hwang, J. Park, K. Park, H. Jeong, Y. Ha, and Y. Hwang, "58.2: Distinguished paper: Implementation of 240 hz 55-inch ultra definition LCD driven by a-IGZO semiconductor TFT with copper signal lines," in *SID Symp. Dig. Tech. Papers*, 2012, vol. 43, no. 1, pp. 784–787.

- [3] P. Barquinha, L. Pereira, G. Gonalves, R. Martins, D. Kuer, M. Kosec, and E. Fortunato, "Performance and stability of low temperature transparent thin-film transistors using amorphous multicomponent dielectrics," *J. Electrochem. Soc.*, vol. 156, no. 11, pp. H824–H831, 2009.

- [4] S. Sambandan, A. Kumar, K. Sakariya, and A. Nathan, "Analogue circuit building blocks with amorphous silicon thin film transistors," *Electron. Lett.*, vol. 41, no. 6, pp. 314–315, Mar. 2005.

- [5] H. Marien, M. Steyaert, E. van Veenendaal, and P. Heremans, "A fully integrated ADC in organic thin-film transistor technology on flexible plastic foil," *IEEE J. Solid-state Circuits*, vol. 46, no. 1, pp. 276–284, Jan. 2011.

- [6] E. Fortunato, P. Barquinha, and R. Martins, "Oxide semiconductor thin-film transistors: A review of recent advances," *Adv. Mater.*, vol. 24, no. 22, pp. 2945–2986, 2012.

- [7] B. Kim, S. C. Choi, J. S. Lee, S. J. Kim, Y. H. Jang, S. Y. Yoon, C. D. Kim, and M. K. Han, "A depletion-mode In-Ga-Zn-O thin-film transistor shift register embedded with a full-swing level shifter," *IEEE Electron Device Lett.*, vol. 58, no. 9, pp. 3012–3017, Sep. 2011.

- [8] D. Raiteri et al., "A 6 b 10 ms/s current-steering DAC manufactured with amorphous gallium-indium-zinc-oxide TFTs achieving SFDR > 30 dB up to 300 kHz," in *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers (ISSCC'2012)*, Feb. 2012, pp. 314–316.

- [9] J. Zhang, X. Li, J. Lu, Z. Ye, L. Gong, P. Wu, J. Huang, Y. Zhang, L. Chen, and B. Zhao, "Performance and stability of amorphous ingazno thin film transistors with a designed device structure," *J. of Appl. Phys.*, vol. 110, no. 8, pp. 084 509–084 509, 2011.

- [10] P. Meijer, "Table models for device modelling," in *IEEE Int. Symp. Circuits Syst.*, 1988, vol. 3, pp. 2593–2596.

- [11] V. B. Litovski, J. I. Radjenović, Ž. M. Mrčarica, and S. L. Milenković, "MOS transistor modelling using neural network," *Electron. Lett.*, vol. 28, no. 18, pp. 1766–1768, Aug. 1992.

- [12] A. Nathan, A. Kumar, K. Sakariya, P. Servati, K. Karim, D. Striakhilev, and A. Sazonov, "Amorphous silicon back-plane electronics for OLED displays," *IEEE J. Sel. Topics Quantum Electron.*, vol. 10, no. 1, pp. 58–69, Jan. 2004.

- [13] L. E. Feller, "Zinc tin oxide thin-film transistor current mirror circuits," Master's thesis, Oregon State Univ., Portland, OR, United States, 2011.

- [14] K. Hornik, M. Stinchcombe, and H. White, "Multilayer feedforward networks are universal approximators," *Neural Netw.*, vol. 2, no. 5, pp. 359–366, 1989.

- [15] P. Barquinha, L. Pereira, G. Goncalves, R. Martins, and E. Fortunato, "Toward high-performance amorphous GIZO TFTs," *J. Electrochem. Soc.*, vol. 156, no. 3, pp. H161–H168, 2009.

- [16] G. Bernardo, G. Goncalves, P. Barquinha, Q. Ferreira, G. Brotas, L. Pereira, A. Charas, J. Morgado, R. Martins, and E. Fortunato, "Polymer light-emitting diodes with amorphous indium-zinc oxide anodes deposited at room temperature," *Synth. Metals*, vol. 159, no. 11, pp. 1112–1115, 2009.

- [17] P. Barquinha, L. Pereira, G. Goncalves, D. Kuscer, M. Kosec, A. Vila, A. Olziersky, J. R. Morante, R. Martins, and E. Fortunato, "Low-temperature sputtered mixtures of high-κ and high bandgap dielectrics for GIZO TFTs," J. Soc. Inf. Display, vol. 18, no. 10, pp. 762–772, Oct. 2010.

- [18] A. Olziersky, P. Barquinha, A. Vila, L. Pereira, G. Goncalves, E. Fortunato, R. Martins, and J. R. Morante, "Insight on the SU-8 resist as passivation layer for transparent Ga<sub>2</sub>O<sub>3</sub>-In<sub>2</sub>O<sub>3</sub>-ZnO thin-film transistors," *J. Appl. Phys.*, vol. 108, no. 6, pp. 064505–064505-7, Sep. 2010.

and neuromorphic integrated-chip design and biomimetic computing, CMOS RF integrated circuit design and transparent electronics. In 2010, he was a Visiting Professor at Carnegie Mellon University, Pittsburgh, PA, USA.

Dr. Tavares is a co-founder and chairman of the Portuguese IEEE Education Society Chapter.

**Pedro Barquinha** was born in 1980. He received the Ph.D. degree in nanotechnologies and nanosciences, with the dissertation "Transparent Oxide Thin-Film Transistors" from Universidade Nova de Lisboa (UNL), Caparica, Portugal, in 2010.

His current research topics are the study of materials for transparent/flexible TFTs and integration in circuits, as well as the nanofabrication of devices using FIB/EBL. He is currently an assistant professor at the Department of Materials Science, Faculty of Science and Technology, Materials Science Depart-

ment, FCT-UNL, Universidade Nova de Lisboa, Caparica, Portugal. Dr. Barquinha won important scientific prizes, such as the "Stimulus to research 2008" (Calouste Gulbenkian Foundation) and Innovation Prize for Young Engineers 2008 (Portuguese Order of Engineers).

Cândido Duarte (S'06) received the Diploma degree in electrical and computer engineering from Faculdade de Engenharia, Universidade do Porto FEUP, Portugal, in 2006.

Since 2009 he has been with the Department of Electrical and Computer Engineering at FEUP as Teaching Assistant in courses of fundamental electronics, measurements, sensors and instrumentation. He is currently working toward the Ph.D. degree in electrical and computer engineering at the same institution. In 2006, he joined INESC Porto, Por-

tugal, where currently works as a researcher. His scientific interests include RF power amplifiers, wireless transceiver architectures, low-power mixed-signal IC design, and CMOS circuits for mobile communications systems.

**Pydi Ganga Bahubalindruni** received the B.Tech. degree in electronics and communications from Jawaharlal Nehru Technical University (JNTU), Hyderabad, India, in 2002, and the M.Tech. degree in electronic instrumentation from and National Institute of Technology (NIT), Warangal, India, in 2007. Following the master's degree, she joined Flowgic India, Chennai, India, as a technical member. Currently she is working toward the Ph.D. degree at FEUP, and a researcher in INESC TEC (formerly INESC Porto), Porto, Portugal.

Her research interests include reconfigurable ASIC design, modeling of semiconductors with neural networks and design of analog signal processing and conditioning circuits with a-GIZO TFTs.

Vítor Grade Tavares received the Licenciatura and M.S. degrees in electrical engineering from the University of Aveiro, Portugal, in 1991 and 1994, respectively, and the Ph.D. degree in electrical engineering, from the Computational NeuroEngineering Laboratory at the University of Florida, Gainesville, FL, USA, in 2001.

In 1999, he joined the University of Porto, Porto, Portugal, as an Invited Assistant, where, since 2002, he has been an Assistant Professor. He is also a Senior Researcher at the INESC TEC (formerly INESC

Porto), Porto, Portugal. His research interests include low power, mixed signal

**Pedro Guedes de Oliveira** is Professor of Electronics at the Faculty of Engineering of the University of Porto (FEUP) and his research interests are in the area of electronic circuits and microelectronics, signal processing and biomedical applications. He was formerly President of INESC Porto and is, at present, head of Electrical and Computer Engineering Department, Universidade do Porto FEUP, Porto, Portugal

**Rodrigo Martins** received the M.Sc. degree in amorphous semiconductor technologies in 1977 from University of Dundee, Dundee, U.K., the Ph.D. degrees in amorphous semiconductors in 1982, and the Ph.D. degree in aggregation in microelectronics, 1988, from New University of Lisbon, Caparica, Portugal, in 1982 and 1988, respectively. He is one of the inventors of the paper electronics.

He is Full Professor in Microelectronics and Optoelectronics since 2001 in the Materials Science Department, Universidade Nova de Lisboa, Caparica,

Portugal, and the head of department since 1996. In 1989, he founded the Centre of Excellence in Microelectronics and Optoelectronics (CEMOP/Uninova) and in 1993, the research materials center, CENIMAT. Presently, he is the running

president of the European Materials Research Society (E-MRS); member of: Academia de Engenharia, Portugal; administration board of Alliance for Materials and EuMat (European dimension structures); Steering Committee of the Sino-Portuguese Joint Innovation Center for Advanced Material established in March 2013; External Advisory Board of the FAME program of the European Multifunctional Institute of University of Bourdeaux, Steering Committee of Energy Materials Industry Research Initiative, EMIRI, an European Platform targeting to be a Public Private Partnership; coordinator of the Portuguese Ph.D. program in Advanced Materials and Processing (AdvaMTech), Doctor Honoris Causa degree by University of Galaty, Romania.

Elvira Fortunato is Professor of Materials Science at the Faculty of Sciences and Technology, Universidade Nova de Lisboa, Caparica, Portugal. She pioneered European research on transparent electronics, namely thin-film transistors based on oxide semiconductors, demonstrating that oxide materials may be used as true semiconductors. In 2008, she won an Advanced Grant from ERC for the project "Invisible" Director of the Materials Research Center. She is Director of the Ph.D. program in Micro and Nanotechnologies Engineering.

Dr. Fortunato is associate editor of Wiley's *Pysica Status Solidi Rapid Research Letters*, a Co-Editor of *Europhysics Letters*, and a Member of the Advisory Editorial Board of *Applied Surface Science*. She is also a Member of the National Scientific and Technological Council, and a Member of "Academia de Engenharia", Portugal.